分析数据高速传输协议

QooIC.com 新闻出处:电子市场 | 发布时间:2011/6/17 17:16:35

1 前言

结合航天应用中高速通信数据处理器的需要,阐明应用Data-Strobe编码进行帧数据传输的好处及特点,对Data-Strobe编解码技术进 行详细介绍,并且给出基于FPGA的解码算法。整个设计在高速数据传输中有很广的应用前景,对工程设计有一定的参考价值。

2 DS编码的特点

DS编码是一种高速数据传输方案。美国IEEE 1355-1995 和IEEE 1394-1995(Firewire)标准 应用了这一方案。欧空局SpaceWire ECSS-E50-12A标准 也采用了这一方案。事实上,DS编码传输方式在高速数据传输中有广阔的应用空间,特别是在星载、飞船载电子设备的数据传输中表现出了抗干扰性强、易于实 现、可靠性高的特点。

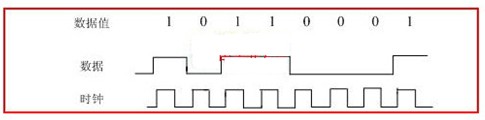

图1 数据-时钟传输方式信号时序图

传统的数据-时钟传输方式是在发送一路数据信号的同时发送出一路时钟信号,接收方根据接收到的时钟来提取数据。如图1所示,这种传输方式的容错范围 是0.5比特时间。在传输过程中,如果受到外界温度等环境因素造成的干扰使数据与时钟传输时间不能严格同步,如果过传输中信号偏差超过0.5比特,则会造 成误码。

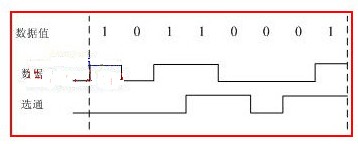

DS编码方式传输的是一路数据信号(DATA)和一路选通信号(STROBE)。应用DS编码,将时钟信号和数据信号进行编码,输出数据信号和选通信号。这样在接收端可以通过对数据和选通两路信号进行简单异或操作来恢复时钟信号。在数据传输中,如果数据信号前后接连两个比 特的值相同,选通信号的状态在传输后一个比特时改变,如果数据信号接连传送的两个比特值不同,那么选通信号在这两个比特时间里保持不变。即在任意两个连续比特数据的间隔处,数据信号与选通信号中只有一个改变状态。如图2所示,相比传统的数据-时钟方式0.5比特时间的容错范围,应用DS编码可将容错范围提高到1比特时间。

图2 Data-Strobe编码信号时序图

3 DS编码技术的实现

在具体应用中,实现DS编码可以有两种方式。这里根据选通信号的产生方式分别称之为串行编码和并行编码。

3.1串行DS编码

串行DS编码是在实现了帧数据比特流串行发送后,将时钟信号进行二分频,然后与数据信号进行异或操作。通过这样的方法产 生选通信号,再将选通信号与数据信号同时发送出去。串行DS编码具有实现简便,应用灵活的特点,适合模块化设计,调试方便。

3.2并行DS编码

并行DS编码是在对数据进行组帧的过程中同步产生DS编码。选通信号并行于数据信号输出。

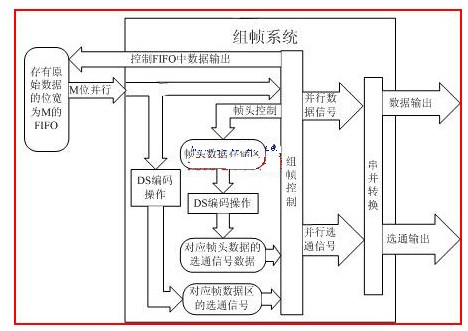

图3 采用并行DS编码的组帧系统结构框图

为了方便说明,在图3中给出采用并行DS编码传输的VCDU帧组建结构图。VCDU即虚拟信道数据单元,它是CCSDS 标准 的数据包(CADU)的一个组成单元。在航天应用中,航天器上各种电子设备分别把各自数据以VCDU 帧形式发送给高速通信处理器,然后由高速通信处理器将各路数据复接为CADU帧。图4显示了数据单元区为886字节的VCDU数据格式。

图4 VCDU数据格式

由图4可见,在VCDU组建过程中,可将其数据格式的前8个字节视为帧头区,后884字节视为帧数据区。如图3所示,帧数据区的数据来自存有原始数 据的缓冲FIFO,帧头区数据在VCDU组建系统中产生。

在用VHDL语言设计并行DS编码中,选通信号的产生不再像串行DS编码那样把串行位流数据与时钟的二分频进行异或操作,而是将以向量形式传来的数 据与一个固定向量进行异或操作。假定图3中FIFO的宽度M为32,对于从输入的32位并行数据进行编码操作是用并行十六进制数“AAAAAAAA”与其 直接进行异或操作。

这种方式产生的选通信号在操作中不受时钟限制,信号的完整性更好。相比于组帧后的串行DS编码,组帧过程中并行编码在结构上略显复杂,整个系统的灵 活性稍差,优点是产生的选通信号稳定,与数据信号完全同步。

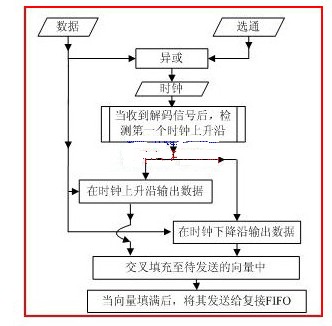

4 DS解码技术

在接收到以DS编码形式传来的数据后,高速通信处理器需要通过进行DS解码得到时钟信号。然后通过该时钟提取出数据,再把数据以向量形式传入复接 FIFO 等待复接。在这里通过DS解码得到的时钟信号,并不是原始的信号,而是在形式上相当于原始时钟的二分频信号。因此,通过用DS解码恢复的时钟来提取数据, 就必须在该时钟的上升沿和下降沿分别取数,然后交叉填充到待输出的向量中。图5是DS解码算法流程图。

图5 DS解码算法流程

5 小结

应用DS编解码的数据传输方式,具有实现简便,容错能力强的特点。根据不同的需要可以在串行DS编码方案和并行DS编码方案间进行选取。近年来随着 微电子技术的不断发展,FPGA的系统时钟频率已经可以达到几百兆赫兹,功耗也有了大幅度的降低,已经在航天工程中得到广泛的应用。通过EDA工具,仅需 要简单的VHDL语言编程,便可以在FPGA中实现组帧及DS编解码等操作。