定时控制电路设计原理

QooIC.com 新闻出处:电子市场 | 发布时间:2011/1/5 14:11:47

电路组成

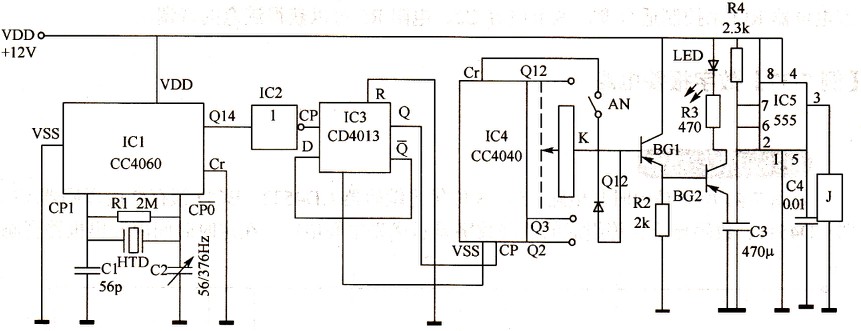

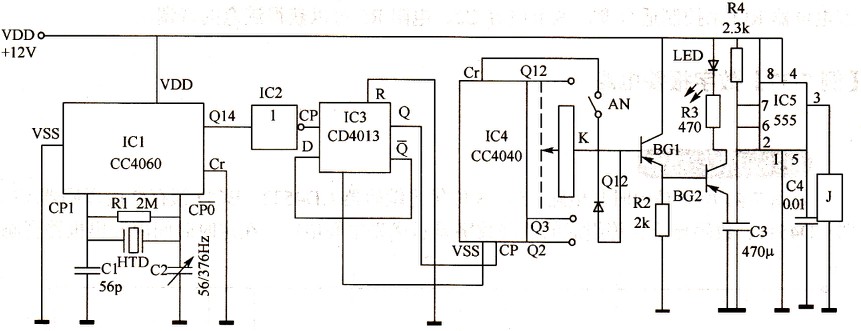

如图1所示是由555定时电路、12位二进制串行计数器/分频器CD4040、双主-从D型触发器CC40i3等组的精密数字式定时控制器。

图1定时控制电路

工作原理

图1中的晶振电路由14位二进制串行计数/分配器(CD4040)、钟表晶体(32768Hz)、C1、C2等组成。晶振信号经CD4060 2"次分频后通过Q14输出,经由IC2反相,再经双D触发器CD4013(IC3)二分频后,得到1Hz的信号,该信号加至IC4的CP端,这个信号用用作时钟控制信号。

IC4为一个12位二进制串行计数/分配器CD4040,当CP信号频率为1Hz时,11个输出端Q4~Q9、Q12~Q14可分别输出2s、4s、8s、16s、32s、64s、128s、2.56s、512s、1 024s、2048s的脉冲,这些脉冲为阶跃高电平。

根据定时的要求,单刀11掷分线开关K将相应的定时阶跃电平引出一路。加至放大器BG1、BG2,经放大后的信号再加至IC5的2脚,使555因2脚处于低电平,置位,3脚输出的高电平使继电器J吸合,接通相应控制的负载,使负载工作。

控制器定时的工作顺序为等待2・溅~11)s后,继电器吸合,接通工作。由于C3通过M进行充电,当C3上的电压使555的6脚电位达到Z/3VDD时,555发生复位,3脚输出的低电平,继电器J释放,相应负载断电,停止工作。

本定时控制器定时时间可从2~2048s,分11个挡次,定时精度高,较一般定时器的理想选择。

如图1所示是由555定时电路、12位二进制串行计数器/分频器CD4040、双主-从D型触发器CC40i3等组的精密数字式定时控制器。

图1定时控制电路

工作原理

图1中的晶振电路由14位二进制串行计数/分配器(CD4040)、钟表晶体(32768Hz)、C1、C2等组成。晶振信号经CD4060 2"次分频后通过Q14输出,经由IC2反相,再经双D触发器CD4013(IC3)二分频后,得到1Hz的信号,该信号加至IC4的CP端,这个信号用用作时钟控制信号。

IC4为一个12位二进制串行计数/分配器CD4040,当CP信号频率为1Hz时,11个输出端Q4~Q9、Q12~Q14可分别输出2s、4s、8s、16s、32s、64s、128s、2.56s、512s、1 024s、2048s的脉冲,这些脉冲为阶跃高电平。

根据定时的要求,单刀11掷分线开关K将相应的定时阶跃电平引出一路。加至放大器BG1、BG2,经放大后的信号再加至IC5的2脚,使555因2脚处于低电平,置位,3脚输出的高电平使继电器J吸合,接通相应控制的负载,使负载工作。

控制器定时的工作顺序为等待2・溅~11)s后,继电器吸合,接通工作。由于C3通过M进行充电,当C3上的电压使555的6脚电位达到Z/3VDD时,555发生复位,3脚输出的低电平,继电器J释放,相应负载断电,停止工作。

本定时控制器定时时间可从2~2048s,分11个挡次,定时精度高,较一般定时器的理想选择。